## 第 58 回

# 業績賞贈呈

(写真:敬称略)

本会選奨規程第9条イ号(電子工学及び情報通信に関する新しい発明,理論,実験,手法などの基礎的研究で,その成果の学問分野への貢献が明確であるもの),口号(電子工学及び情報通信に関する新しい機器,又は方式の開発,改良,国際標準化で,その効果が顕著であり,近年その業績が明確になったもの),ハ号(電子工学及び情報通信並びに関連する分野において長年にわたる教育の質向上に資する教育施策の遂行,教育の実践(教育法,教材等の開発を含む),著述及びその普及を通じて,人材育成への貢献が明確になったもの)による業績に対し,下記の7件を選び贈呈した.

## 10 ペタビット級超大容量空間多重光伝送 基盤技術の先駆的研究

受賞者 森田逸郎

受賞者 釣谷剛宏

受賞者 相馬大樹

インターネットによる動画像配信や 5G に代表される大容量通信サービスを高品質に提供するため、通信網の基盤である光通信システムには、伝送容量をニーズに応じて持続的に拡大できる容量の拡張性が求められる。しかし、単一のコアを有する従来の光ファイバを用いた伝送システムでは、光ファイバへ入力可能な光信号パワーの制限等により、伝送容量は 100 Tbit/s (0.1 Pbit/s)程度に物理的限界があることが判明していた。これは、最新の商用伝送システムの最大伝送容量の 10 倍程度でしかなく、年率約 40% の通信トラヒックの増加(10 年で約 30 倍)を考慮すると十分ではなく、従来技術の限界を打破し持続的かつ飛躍的に容量拡大が可能な新技術が求められていた。

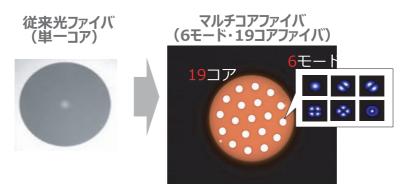

以上の背景から、伝送媒体である光ファイバを見直 し、光ファイバ中に複数のコアを有するマルチコアファ イバや複数の独立伝搬モードを伝搬させる多モードファ イバを用いる空間多重光伝送技術の研究が2010年頃か ら国内外で活発に開始された(1). 受賞者らは、従来技術 の限界を明確化した上で空間多重光伝送技術に先導的に 取り組み(2), 2012年の世界初のマルチコアファイバに よる大洋横断級伝送(3), 2013年の世界最大の容量距離 積 1 Ebit/s×km(エクサ=10<sup>19</sup>=1,000 ペタ)の実証(4) により、干渉抑圧型マルチコアファイバのコア多重数に 比例した容量拡大の可能性を実験的に実証した. その 後、干渉抑圧マルチコアファイバの各コアを多モード化 することで、空間多重数 (コア数×モード数) の更なる 拡大を図った。図1に示す空間多重数が100を超える多 モード・マルチコアファイバによる大容量化を進 め<sup>(5), (6)</sup>, 2017年に既存の最新商用光伝送システムの約 1,000 倍の容量に相当し、従来の単一コアの光ファイバ にて報告されている最大容量の約100倍に相当する 10 Pbit/s の超大容量伝送に世界で初めて成功した(図 2). これは、ファイバ通信の伝送容量が「京」の領域に 到達可能であることを世界で初めて実証した実験であ る 6. これらの一連の世界初の実証に基づく基礎研究 は、時分割多重、偏波多重、波長多重、直交振幅多重の 次に期待される光波の新たな直交軸での多重化技術とし て,空間多重技術が持続的な容量拡大に極めて有効であ ることを示した. 更に、その早期実用化のために、既存 光通信システムとの互換性を考慮し、コア数やコア配置 を最適化した標準外径のマルチコアファイバの敷設状態 での特性評価<sup>(7)</sup>や1万km以上の長距離伝送評価<sup>(8)</sup>を実 施し、その実用化を見据えた研究も推進した。

受賞者らはその初期段階から空間多重光伝送方式の研究を精力的に推進し,光ファイバ通信における空間多重 の多重化技術としての潜在的可能性を実証する世界初の

図1 光ファイバの断面写真

図2 光ファイバ伝送容量の推移

成果を継続的に示すことで、新しい空間多重光伝送の開拓において世界をけん引した。受賞者らの業績は、光通信システムの大容量化に対する持続可能性を実証した先導的・先駆的な基礎的研究として学術的貢献が極めて大きく、著名な国際会議から数多くの招待講演を受けるなど世界中から高い評価を得ている。現在では、空間多重方式は超大容量光伝送のための主要技術として世界中で認知されており、本業績は、我が国の研究開発力を国際的にアピールする基礎研究として影響度と波及効果が極めて大きい顕著なものである。

以上のように、受賞者らの業績は極めて顕著であり、 本会業績賞にふさわしいものである.

#### 文 煎

- (1) 中沢正隆, 鈴木正敏, 盛岡敏夫, 光通信技術の飛躍的高度化-光通信の新たな挑戦--, オプトロニクス社, 東京, 2012.

- (2) I. Morita and M. Suzuki, "Innovations for future optical submarine cable systems," OECC2010, 6B2-4, 2010.

- (3) H. Takahashi, T. Tsuritani, E.L.T. de Gabory, T. Ito, W.-R. Peng, K. Igarashi, K. Takeshima, Y. Kawaguchi, I. Morita, Y. Tsuchida, Y. Mimura, K. Maeda, T. Saito, K. Watanabe, K. Imamura, R. Sugizaki, and M. Suzuki, "First demonstration of MC-EDFA-repeatered SDM transmission of 40 x 128-Gbit/s PDM-QPSK signals per core over 6,160-km 7-core MCF," ECOC2012, Th3C. 3, 2012.

- (4) K. Igarashi, T. Tsuritani, I. Morita, Y. Tsuchida, K. Maeda, M. Tadakuma, T. Saito, K. Watanabe, K. Imamura, R. Sugizaki, and M. Suzuki, "1.03-Exabit/skm super-Nyquist-WDM transmission over 7,326-km seven-core fiber," ECOC2013, PD3. E. 3, 2013.

- (5) D. Soma, K. Igarashi, Y. Wakayama, K. Takeshima, Y. Kawaguchi, N. Yoshikane, T. Tsuritani, I. Morita, and M. Suzuki, "2.05 Peta-bit/s super-nyquist-WDM SDM transmission using 9.8-km 6-mode 19-core fiber in full C band," ECOC2015, PDP3.2, 2015.

- (6) D. Soma, Y. Wakayama, S. Beppu, S. Sumita, T. Tsuritani, T. Hayashi, T. Nagashima, M. Suzuki, H. Takahashi, K. Igarashi, I. Morita, and M. Suzuki, "10.16 peta-bit/s dense SDM/WDM transmission over low-DMD 6-mode 19-core fibre across C+L band," ECOC2017, Th. PDP.A. 1, 2017.

- (7) T. Tsuritani, D. Soma, Y. Wakayama, Y. Miyagawa, M. Takahashi, I. Morita, K. Maeda, K. Kawasaki, T. Matsuura, M. Tsukamoto, and R. Sugizaki, "Field test of installed high-density optical fiber cable with multi-core fibers toward practical deployment," OFC2019, M3J. 4, 2019.

- (8) D. Soma, S. Beppu, H. Takahashi, N. Yoshikane, I. Morita, and T. Tsuritani, "Performance comparison of standard cladding ultra-low-loss uncoupled and coupled 4-core fibres transmission over 15,000 km," ECOC2020, Mo2E. 4, 2020.

## 剰余系表現(RNS)を用いた公開鍵暗号の 実装に関する先駆的研究

受賞者 川村信一

受賞者 駒野雄一

情報化社会のセキュリティ実現に公開鍵暗号は不可欠である。受賞者らは公開鍵暗号を、剰余系表現(RNS)を用いて演算する効率的な基本アルゴリズムを提案し、通常のバイナリー表現よりも並列性に優れた暗号実装を実現した。受賞者らは、近似計算を導入することでRNSでは効率良く計算できなかった剰余算と大小比較を厳密かつ効率的に計算する基本アルゴリズムを提案し、RNSを用いた公開鍵暗号の実装という新しい研究分野の開拓に貢献した。

研究対象である RNS は、整数表現の一つで、整数 x を基底要素で割った余り n 個の組で表す(図 1(a))。 隣接要素へのキャリー(桁上がり処理)が生じないため、加・減・乗算は小さい整数の独立した n 回の加・減・乗算に容易に分解できる。同一構成の演算器を n 個用

意すれば n 倍に高速化できる。このような利点を持つ 反面,RNS では整数 x の大きさの評価が困難なため除 算(剰余算)と大小比較が効率的に行えない。そのため RNS の実用的な応用は 2000 年以前にはほぼ皆無だった。

受賞者らは、多くの公開鍵暗号が、数百~数千ビットという巨大な整数で構成されることに着目し、RNSを用いて例えば 1,024 ビットの整数演算を 32 ビットの基底を用いて 32 並列で効率的に処理できるのではないかと考えた、課題解決のポイントは、RNS 表現された整数 x の大きさを直接求めるのではなく、相対値 x/M に着目し、そのビット列を近似計算して x の大きさを評価する方法を提案したことである。ただし、M は RNS の基底要素の積で、表現できる整数の範囲を表す。

#### (1) 剰余算の提案

RNS でx を値p で割った剰余を求める処理には,図1 (b)の式(1)により x/M を評価する演算が現れる.従来はこの演算に乗算器を用いる必要があり,回路規模が大きいことが実用化の妨げとなっていた.そこで,式(1)を最適化することにより,この問題を関数 Fr の入力と出力の差分である整数部を評価する問題に帰着させ,入力の各項を上位数ビットで近似して整数部を加算で求める方法を提案した(式(2)).これにより回路規模を従来の十分の一以下に削減して実用化への道を開いた.更に提案方式を剰余乗算に適用して RSA 暗号の LSI 実装や改良を進め,乗算回数最少の方式を実現した $^{(1)\sim(4)}$ .

#### (2) 大小比較の提案

基底: $\{m_1, m_2, m_3\} = \{3, 5, 7\}$

整数の大小比較は 2 数の差をとり結果の正負で判断できる. x/M の小数点以下第 1 ビットを負の数を表す符号ビットと定義すると,前記の近似法を拡張して符号判定を構成できる. ほとんどの整数は上位 1 ワードまでの近似で符号を決定でき,極めてまれに近似精度が不足す

基底:

$$\{m_1, m_2, m_3\} = \{3, 5, 7\}$$

レンジ: $M = m_1 m_2 m_3 = 3 \cdot 5 \cdot 7 = 105$

RNS表現 $\vec{x}$ :

$x (0 \le x \le M - 1 = 104)$ に対して、

$\vec{x} = [(x)_3, (x)_5, (x)_7]$

但し、 $(x)_m = x \mod m$  と定義。

数値例:

$$\overrightarrow{94} = [(94)_3, (94)_5, (94)_7] = [1, 4, 3]$$

$\overrightarrow{6} = [(6)_3, (6)_5, (6)_7] = [0, 1, 6]$

$\overrightarrow{94} + \overrightarrow{6} = [(1+0)_3, (4+1)_5, (3+6)_7]$

$= [1, 0, 2]$

(a) RNSの数値例

基底で定まる正規化行列Aと中間表現v: [2 0 0] 0 1 0  $\vec{y} = \vec{x} A$ Lο 0 1. る関数とすると: Frは小数部を与え (1) $m_1$ 数值例:  $\vec{x} = \overrightarrow{94} = [1,4,3]$ の時、 $\vec{y} = [2,4,3]$ 。従って,  $(1) = 0.89 \cdots (2)$ (b) x/Mの近似計算例

図1 RNS を用いた演算

表 1 大小比較方式の性能(5)

|       | 平均計算<br>ステップ数* | 演算幅<br>(ビット)                                                         | メモリ量                             |

|-------|----------------|----------------------------------------------------------------------|----------------------------------|

| 提案方式  | $O(\log_2 n)$  | $\lceil \log_2 m_i \rceil$                                           | $O((\log_2 M)^2)$                |

| 従来方式1 | $O(\log_2 n)$  | $ \lceil \log_2 n\Phi \rceil $ $ \approx \lceil \log_2 nm_i \rceil $ | $\approx O((\log_2 M)^3)$        |

| 従来方式2 | $O(\log_2 n)$  | [log <sub>2</sub> nM]                                                | $O(M^{\frac{1}{n}}(\log_2 M)^2)$ |

\*演算ユニットはn並列の整数演算器と仮定 色付のセルは提案方式より劣る項目

る場合のみ近似精度を上げることで、最も省リソースの符号判定(大小比較)が実現できた(表 1). これはメモリ量最少で漸近的に最適な計算量を実現し、RNSの工学応用が始まって以来未解決の問題に一つの解を与えた⑤.

#### (3) 新しい研究分野の開拓

RNS は並列性に優れ処理速度・低消費電力でバイナリーを凌駕する場合も多く、専用 LSI や FPGA のほか、市場拡大が著しい GPU との相性も良いため一層の発展が期待できる (6) 論文 (1) の発表以後、RNS の暗号応用論文が増加し、論文 (1) は現在同分野の論文の 45% で引用されている。また解説論文 (6)  $\sim$  (8) や教科書 (9)  $\sim$  (10) で、論文 (1) は RNS の暗号応用を考える上で不可欠の論文と高く評価されている。提案方式は、基底集合サイズ n に関してスケーラブルで汎用性が高く今後の鍵長の延長にも容易に対応できる。近年受賞者らの提案は、サイドチャネル撃対策や最新の格子暗号・準同形暗号等にも応用されている (6)  $\sim$  (8)

これらの基礎的研究は、RNSを用いた公開鍵暗号の 実装という新しい研究分野の確立に貢献し、業績賞にふ さわしい成果である。

#### 文 献

- S. Kawamura, M. Koike, F. Sano, and A. Shimbo, "Cox-rower architecture for fast parallel Montgomery multiplication," EURO-CRYPT2000, Lect. Note Comput. Sci., vol. 1807, Springer, May 2000.

- (2) H. Nozaki, M. Motoyama, A. Shimbo, and S. Kawamura, "Implementation of RSA algorithm based on RNS Montgomery multiplication," CHES 2001, Lect. Note Comput. Sci., vol. 2162, Springer, Sept. 2001.

- (3) H. Nozaki, A. Shimbo, and S. Kawamura, "RNS Montgomery multiplication algorithm for duplicate processing of base transformations," IEICE Trans. Fundamentals, vol. E86-A, no. 1, pp. 89-97, Jan. 2003

- (4) S. Kawamura, Y. Komano, H. Shimizu, and T. Yonemura, "RNS Montgomery reduction algorithms using quadratic residuosity," Journal of Cryptographic Engineering, vol. 9, no. 4, Springer, Nov. 2019.

- (5) S. Kawamura, Y. Komano, H. Shimizu, S. Osuka, D. Fujimoto, Y. Hayashi, and K. Imafuku, "Efficient algorithms for sign detection in RNS using approximate reciprocals," IEICE Trans. Fundamentales, vol. E104-A, no. 1, pp. 121-134, Jan. 2021.

- (6) L. Sousa, S. Antao, and P. Martins, "Combining residue arithmetic to design efficient cryptographic circuits and systems," IEEE Circuit and Systems Magazine, vol. 16, no. 4, pp. 6-32, Nov. 2016.

- (7) D. Schoinianakis, "Residue arithmetic systems in cryptography: a survey on modern security applications," Journal of Cryptographic Engineering, vol. 10, pp. 249-267, June 2020. DOI: https://doi.org/ 10.1007/s13389-020-00231-w

- (8) J.C. Bajard, J. Eynard, and N. Merkiche, "Montgomery reduction within the context of residue number system arithmetic," Journal of Cryptographic Engineering, vol. 8, no. 3, pp. 189-200, Sept. 2018.

- (9) P.V. Ananda Mohan, "Residue number systems, theory and applications," RNS Montgomery Multiplication and Exponentiation, Sect. 10.3, pp. 287-295, Springer, 2016.

- (10) "Embedded systems design with special arithmetic and number systems," A.S. Molahosseini, L.S. de Sousa, and C.-H. Chang, eds., in Chapter 2 and Chapter 12, Springer, 2017.

## 光ファイバ非線形性の通信応用に関する 先駆的研究

受賞者 並木 周

世界の情報通信の根幹を支える光ファイバは石英をベースとした光導波路であり、そこを伝搬する光信号は損失・分散に加え、三次の非線形光学効果を受ける。光信号の高ビットレート化で問題となるこれらの影響をいかに克服して、光ファイバ当りの伝送容量・距離を極限まで増大するかは重要な課題であった。受賞者の並木周氏は、これまで30年にわたり、主に光ファイバの非線形性を活用した、光ファイバの損失・群速度分散・非線形性の独創的な補償技術を創出するとともに、それらの実用化にも尽力してきた。その結果、多くの共同研究者とも連携し数々の先駆的業績を上げた。中でも特筆すべき点は、ラマン増幅及び四光波混合の広帯域化・波長可変性に関して重要な発明を行い、それぞれの実用化に大きく貢献したことである。

受賞者は、1990年代前半に当時世界最高出力の励起レーザの量産実装技術の開発を主導し、その後3年間MIT(Massachusetts Institute of Technology)で超短光パルスの動的振舞いや量子雑音観測に関する研究に従事した。これらの経験を生かし、100 nm という広帯域にわたり平たんな利得を実現する波長多重励起方式によるラマン増幅器を発案・共同発明し、実用化を主導した(①.②。この方式は、その広帯域性・低雑音性により、現在光通信の大容量化・長距離化に重要な基盤技術として世界で広く利用され、インターネットの進展を支えている。

また、光ファイバ中の四光波混合を広帯域で発生する方式を発案・共同発明し<sup>(3)</sup>、高非線形ファイバの商用化及びその特性改善に大きく貢献した。特に、高非線形ファイバの分散スロープを抑制しゼロ分散波長の位置を最適化することで、従来、励起光波長をゼロ分散波長近傍に固定しなければならなかった縮退四光波混合においても、位相整合条件を損なうことなく励起光波長を広帯域にわたって可変できることを示した<sup>(4)</sup>。これにより簡便で高品質な波長可変四光波混合装置が実現され、以下に例示する様々な研究の礎となった。まず、四光波混合

による可変波長変換と分散媒質を組み合わせることで、THz級の超広帯域光信号に対して群速度分散と遅延を独立かつ連続的に制御する方式を発明(5).(6)した.従来の分散/遅延補償方式は光の干渉効果を利用するため原理的に帯域と分散/遅延量がトレードオフの関係にあるのに対して、本方式は根本的に異なる原理に依拠するため、10~100倍の性能指数向上を達成している.更に、位相感応形光増幅の効率を飛躍的に向上する手法(で)や、波長分割多重信号が相互に受ける非線形ひずみを光のまま補償する技術で、10dBという従来方式より大幅に大きな非線形しきい値改善率を実証(8)し、非線形シャノン限界の克服に一石を投じるなど、数多くの研究成果を上げた.

以上のように、受賞者は、それまで基礎研究の域にあった光ファイバ非線形性の応用技術を開拓・発展させ、実用レベルに高めることに大きく貢献した。その一部は商用化され世界に普及している。これらの業績は海外からも高く評価され、受賞者は国際会議等で100件以上の招待講演を行うのみならず、国際会議運営委員会などでの各種の要職に数多く携わってきた。中でも、光ファイバ通信分野で世界最大かつ最も権威ある国際会議OFC(The Optical Networking and Communication Conference & Exhibition)においてはジェネラルチェアを務めている。以上述べたように、受賞者の功績は極めて顕著であり、本会業績賞にふさわしいものである。

#### 文献

- (1) S. Namiki, N. Tsukiji, and Y. Emori, "Pump laser diodes and WDM pumping," in Raman Amplifiers For Telecommunications 1, M. Islam, ed., Chapter 5, pp. 121-160, Springer-Verlag, 2004.

- (2) S. Namiki and Y. Emori, "Ultrabroad-band Raman amplifiers pumped and gain-equalized by wavelength-division-multiplexed high-power laser diodes," IEEE J. Sel. Top. Quantum Electron., vol. 7, no. 1, pp. 3-16, Jan./Feb. 2001.

- (3) O. Aso, S. Arai, T. Yagi, Y. Suzuki, and S. Namiki, "Broadband four-wave mixing generation in short optical fibers," Electron. Lett., vol. 36, no. 8, pp. 709-711, 2000.

- (4) S. Namiki, T. Kurosu, K. Tanizawa, S. Petit, M. Gao, and J. Kurumida, "Controlling optical signals through parametric processes," IEEE J. Sel. Top. Quantum Electron., vol. 18, no. 2, pp. 717-725, 2012.

- (5) S. Namiki, "Wide-band and-range tunable dispersion compensation through parametric wavelength conversion and dispersive optical fibers," J. Lightwave Technol., vol. 26, no. 1, pp. 28-35, 2008.

- (6) T. Kurosu and S. Namiki, "Continuously tunable 22 ns delay for wideband optical signals using a parametric delay-dispersion tuner," Opt. Lett., vol. 34, 1441, 2009.

- (7) M. Gao, T. Inoue, T. Kurosu, and S. Namiki, "Evolution of the gain extinction ratio in dual-pump phase sensitive amplification," Opt. Lett., vol. 37, no. 9, pp. 1439-1441, 2012.

- (8) S. Namiki, K. Solis-Trapala, H. Nguyen Tan, M. Pelusi, and T. Inoue, "Multi-channel cascadable parametric signal processing for wavelength conversion and nonlinearity compensation," J. Lightwave Technol., vol. 35, no. 4, pp. 815-823, 2017.

### 5G 通信システムにおけるミリ波防護に関する 先駆的研究と国際標準化

受賞者 平田晃正

受賞者 渡辺聡一

第5世代移動通信システム(5G)は、従来の携帯電 話システムよりも高い、ミリ波帯を含む 6GHz 以上の周 波数の電波を利用することで、その特徴である超高速・ 大容量通信を実現している. この新規周波数領域の電波 を,一般公衆の生活環境へ導入するに先立ち,5Gシス テムを安心・安全かつ有効に利用するための電波への人 体ばく露の防護に関心が持たれていた。世界保健機関 (WHO) が推奨する電波への人体ばく露の防護のため の国際ガイドラインである IEEE 国際規格及び国際非電 離放射線防護委員会 (ICNIRP) ガイドラインでは、従 来, 3~10 GHz 以上の周波数帯における知見の欠如か ら, 暫定的な指標を用いて, 過度に安全側の防護基準値 を示していた. そのため、従来の国際ガイドラインの電 波ばく露の防護基準値の範囲において, ミリ波帯の携帯 無線端末を人体近傍で使用することはほぼ不可能であ り、科学的根拠に基づいたミリ波帯での新防護基準の策 定が求められていた.

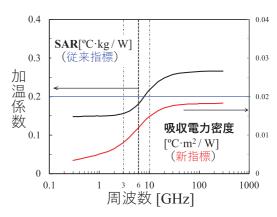

電波ばく露の新しい防護基準値を設定するにあたり、 人体がミリ波にさらされた際の組織中の電波吸収に起因する人体の温度上昇特性とその温度上昇を決定付ける物理指標の明確化が課題であった。受賞者(渡辺、佐々木)らは、人体の電波吸収特性の評価において必須の人体を構成する皮膚や脂肪、筋肉等の様々な組織の電気的な応答を示す基礎定数(電気定数)の計測技術を開発し、従来周波数帯から1THzにわたる超広帯域での組織電気定数の実測に成功した<sup>(1),(2)</sup>。また、受賞者(平田)は、電磁気・熱伝導の複合物理に加え、人体の生理学的温熱調整系を考慮した計算手法を開発した<sup>(3)</sup>。

これらの基盤的かつ先駆的な研究成果に基づいて、受

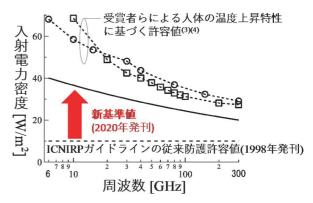

図1 従来のガイドラインで 3-10 GHz までの基準値の指標である 比吸収率(SAR (W/kg))と新たな指標である吸収電力密度による加温係数(単位当りの温度上昇値) 6 GHz 以上では吸収電力 密度が周波数に依存しない評価指標 <sup>(5)</sup>.

図2 入射電力密度の防護許容値の周波数特性

賞者らは、人体の体表がミリ波帯の電波にさらされた際の吸収電力量と人体の温度上昇との関係性を詳細に明らかにした。具体的には、周波数・アンテナ等の電波の発射条件に依存せず、電波ばく露時の温度上昇特性と優れた相関を有する新たな評価指標として「吸収電力密度」を考案し(4).(5)、携帯電話システムの従来周波数帯と整合の取れた防護基準値を明らかにした(図1)。そして、電波ばく露による人体の温度上昇特性と物理的な相関を持つ吸収電力密度の基準値に基づき、実際の5G端末等に対して計測可能な物理量である入射電力密度の防護許容値を明らかにした(図2)(3).(4). 更に、我が国固有の眼球に特化した防護基準に着目し、医学研究グループとの連携により、うさぎの眼球へのばく露において実測値との比較による計算値への信頼性を担保し(6)、眼球を特別扱いする必要がないことも示した.

受賞者らは ICNIRP や IEEE における国際標準化機関並びに国内制度化において、当該部門委員長、主査など要職を務め、国内外の 5G システムの円滑な導入に貢献した、特に、世界に先駆けて制度化された我が国における新防護基準 (2018 年) の根拠は、その後に策定され

た IEEE 国際規格(2019 年)及び ICNIRP ガイドライン(2020 年)でも採用されている<sup>①</sup>. 発刊当初からお互いに整合した前例がない IEEE と ICNIRP が、新防護基準において規格整合に至ったのは、受賞者らにより考案された一貫性ある根拠が両機関に高く評価されたものである。

以上のように、受賞者らはばく大な経済効果と SDGs を実現する Society 5.0 のインフラ基盤となることが見込まれている 5G の世界的な導入・普及において、その防護基準の国際標準化に決定的な貢献をしたことから、その功績は顕著であり、本会業績賞にふさわしいと認められる.

#### 文 献

(1) K. Sasaki, Y. Isimura, K. Fujii, K. Wake, S. Watanabe, M. Kojima, R. Suga, and O. Hashimoto, "Dielectric property measurement of ocular tissues up to 110 GHz using 1 mm coaxial sensor," Phys. Med. Biol.,

- vol. 60, no. 16, pp. 6273-6288, Aug. 2015.

- (2) K. Sasaki, M. Mizuno, K. Wake, and S. Watanabe, "Monte Carlo simulations of skin exposure to electromagnetic field from 10 GHz to 1 THz," Phys. Med. Biol., vol. 62, no. 17, pp. 6993-7010, Aug. 2017.

- (3) S. Kodera, J. Gomez-Tames, and A. Hirata, "Temperature elevation in the human brain and skin with thermoregulation during exposure to RF energy," Biomed. Eng. Online, vol. 17, no. 1, Jan. 2018.

- (4) Y. Hashimoto, A. Hirata, R. Morimoto, S. Aonuma, I. Laakso, K. Jokela, and K.R. Foster, "On the averaging area for incident power density for human exposure limits at frequencies over 6 GHz," Phys. Med. Biol., vol. 62, no. 8, pp. 3124-3138, April 2017.

- (5) D. Funahashi, A. Hirata, S. Kodera, and K.R. Foster, "Area-averaged transmitted power density at skin surface as metric to estimate surface temperature elevation," IEEE Access, vol. 6, pp. 77665-77674, Nov. 2018

- (6) K. Sasaki, T. Sakai, T. Nagaoka, K. Wake, S. Watanabe, M. Kojima, N. Hasanova, H. Sasaki, K. Sasaki, Y. Suzuki, M. Taki, Y. Kamimura, A. Hirata, and H. Shirai, "Dosimetry using a localized exposure system in the millimeter-wave band for in vivo studies on ocular effects," IEEE Trans. Microw. Theory Tech., vol. 62, no. 7, pp. 1554-1564, July 2014.

- (7) 佐々木謙介,大西輝夫,渡辺聡一,平田晃正,"5Gシステムからの電波への人体ばく露の防護,"信学誌,vol. 103, no. 12, pp. 1234-1238, Dec. 2020.

## 車載画像認識プロセッサ Visconti™ の 研究開発と実用化

受賞者 渡辺友樹

受賞者 岡田隆三

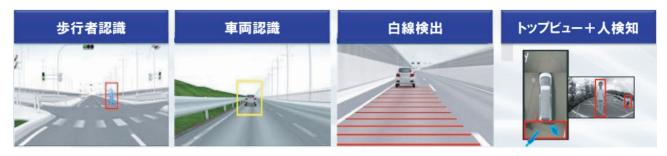

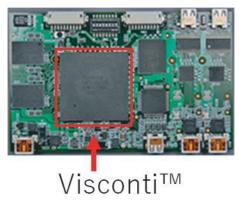

自動車の自動緊急ブレーキ(AEB)等の安全運転支援機能に必要な、車載カメラによる道路環境認識(図1)を実現する画像認識プロセッサ Visconti (図2)を、世界に先駆けて開発し実用化した。画像認識による世界トップレベルの精度を実現した障害物・歩

行者検出アルゴリズム<sup>(1).(2)</sup>と、それを汎用 CPU の数十分の一の低消費電力でリアルタイム処理する処理能力の高いハードウェア<sup>(3)~(6)</sup>を開発した。低電力化により、小形で故障しにくく低コストのカメラー体型システムが実現可能となった。

受賞者らの開発した画像認識プロセッサ Visconti ファミリは, 各世代において先進的な技術を搭載してい る. 2003 年発売の初代 Visconti (3) では、1 台のカメラで 立体障害物を判別するアルゴリズム(1)を考案しリアルタ イム動作させ, コンピュータビジョンの最高峰の国際会 議でその先進性が高く評価された。2011 年発売の Visconti 2<sup>(4)</sup>は、車載向け LSI で世界初となる多種類 (5 種 類)の画像処理専用ハードウェアを搭載した.中でも, HOG アクセラレータは、カメラ画像中の物体形状を詳 細に記述できる独自開発の画像特徴量 CoHOG<sup>(2)</sup>によ り,世界一の歩行者検出性能を実現した.登録特許も多 数保有しており、関東地方発明表彰発明奨励賞や発明協 会東京優秀賞を受賞した特許も保有している。2016年 発売の最新の Visconti 4<sup>(5)</sup>は、時系列画像による三次元 計測技術やカラー画像による歩行者検出などの専用ハー ドウェアを備え, 搭載車は国土交通省所管の公的な自動 車安全テスト (INCAP:自動車アセスメント予防安全 性能評価)で、歩行者の飛び出しを検知して車両を停止 するなどの全項目で満点を獲得し、優位性が公的に認定 されている<sup>(6)</sup>. 次世代の Visconti 5<sup>(7)</sup>は、画像認識 AI プロセッサとして深層ニューラルネットワークの推論 ハードウェア等を新規搭載し、安全運転支援を発展させ

(注1) Visconti は商標.

図1 車載カメラによる道路環境認識の例

図2 画像認識プロセッサ Visconti

た自動運転だけでなく,無人搬送車 (AGV),監視カメラ等の産業分野への展開も期待される.

実用面においても、これらの技術は国内の自動車メーカから高く評価され、多くの自動車に搭載されており、車載カメラ向け LSI 分野のシェアでは、日本メーカで最高位の世界 4 位となっている。今後は、日本や欧州で2021 年から新車への AEB の搭載が段階的に義務化されており、市場予測®も年平均成長率が20%超と、今後需要の増加が見込まれている。

受賞者らの開発した画像認識アルゴリズム及び Visconti ファミリは、その技術的な先進性及び有効性が、主要国際会議や論文採択、各種受賞という形で、国内外で高く評価されている。更に実用化においても Visconti

ファミリは国内の多数の自動車に搭載され、自動車交通 の安全に大きく貢献しており、その業績は極めて顕著で あり、本会業績賞にふさわしいものである.

#### 文 煎

- (1) R. Okada, Y. Taniguchi, K. Furukawa, and K. Onoguchi, "Obstacle detection using projective invariant and vanishing lines," IEEE ICCV, pp. 330-337, Oct. 2003.

- (2) T. Watanabe, S. Ito, and K. Yokoi, "Co-occurrence histograms of oriented gradients for human detection," IPSJ Trans. on CVA, vol. 2, pp. 39-47, March 2010.

- (3) J. Tanabe, Y. Taniguchi, T. Miyamori, Y. Miyamoto, H. Takeda, M. Tarui, H. Nakayama, N. Takeda, K. Maeda, and M. Matsui, "Visconti: Multi-VLIW image recognition processor based on configurable processor," IEEE CICC, pp. 185-188, Sept. 2003.

- (4) Y. Tanabe, M. Sumiyoshi, M. Nishiyama, I. Yamazaki, S. Fujii, K. Kimura, T. Aoyama, M. Banno, H. Hayashi, and T. Miyamori, "A 464GOPS 620GOPS/W heterogeneous multi-core SoC for image-recognition applications," IEEE ISSCC, pp. 222-223, Feb. 2012.

- (5) J. Tanabe, T. Sano, Y. Yamada, T. Watanabe, M. Okumura, M. Nishiyama, T. Nomura, K. Oma, N. Sato, M. Banno, H. Hayashi, and T. Miyamori, "A 1.9TOPS and 665GOPS/W heterogeneous multi-core SoC with color-based object classification accelerators for image recognition applications," IEEE ISSCC, pp. 1-3, Feb. 2015.

- (6) https://toshiba.semicon-storage.com/jp/company/news/news-topics/ 2020/06/automotive-20200612-1.html

- (7) Y. Yamada, T. Sano, Y. Tanabe, Y. Ishigaki, S. Hosoda, F. Hyuga, A. Moriya, R. Hada, A. Masuda, M. Uchiyama, T. Koizumi, T. Tamai, N. Sato, J. Tanabe, K. Kimura, R. Murakami, and T. Yoshikawa, "A 20.5TOPS and 217.3GOPS/mm² Multicore SoC with DNN accelerator and image signal processor complying with ISO26262 for automotive applications," IEEE ISSCC, pp. 132-134, Feb. 2019.

- $(\ 8\ ) \quad \text{https://www.alliedmarketresearch.com/adas-market}$

## 新計算機アーキテクチャ 「デジタルアニーラ」の研究開発と実用化

受賞者 柴﨑崇之

受賞者 米岡 昇

様々な分野の実問題には「組合せ最適化問題」が含まれている。しかし、組合せ数が膨大なため、従来のコンピュータでは実用的な時間で解くことができなかった。そのため、組合せ最適化問題を高速に解くことができる量子コンピュータが注目されている。だが、現行の量子コンピュータでは扱える問題の規模が小さく、また安定性でも課題があるため、複雑な実問題を幅広く扱えるようになるには数年以上かかるとされている。

そこで受賞者らは、量子現象に着想を得ながら、現行のディジタル技術を用い、組合せ最適化問題に特化した新しい計算機アーキテクチャ「デジタルアニーラ」を開発した(1)~(5).

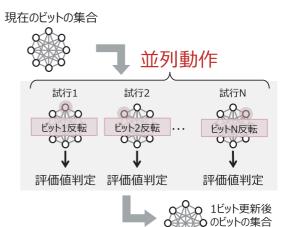

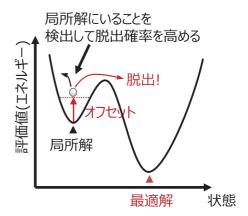

デジタルアニーラは、量子現象に着想を得たディジタ ル回路をコンピュータに付加することで、通常のコン ピュータでは実用的な時間で解けない組合せ最適化問題 を高速で解くことができる. 量子現象には, 「0」と「1」の 二つの異なる状態が同時に出現する「重ね合わせ」があ る. デジタルアニーラでは、 乱数発生器を使って [0] と 「1」の揺らぎのような状態を表現し、評価値(エネル ギー) が下がる方向ヘビットを反転させながら解の探索 を行う.しかし、評価値が下がる方向への遷移だけではそ れ以上評価値が改善しない局所解に捕らわれてしまう. そこで、評価値が悪化する方向へも確率的に遷移するこ とを許容することで局所解から脱出させている. このよう な確率的遷移を並列動作させることで、量子コンピュー タと同様の並列化・高速化を実現している(図1).また. 局所解に捕らわれていることを検知してオフセット値を 与えることで、ビット反転確率を高めて局所解からの脱 出確率を高め、更なる高速化を実現している(図2)、

図1 並列動作による高速化

反転したビット

図2 オフセット付加による高速化

デジタルアニーラは、上記の演算を行う専用ハードウェア(通常のコンピュータと専用回路)と、その制御ソフトウェアから成る。2018年5月にクラウドサービスを開始した第1世代では、問題を定式化(実問題の数学的問題への置き換え)する際に使える変数の個数(個々の変数のビット幅は1)が1,024個だったが、2018年12月にサービスを開始した第2世代では8,192個まで拡大した。この第2世代のデジタルアニーラをコアとした求解技術により実問題への適用を可能とした。

・事例 1:金融(https://pr.fujitsu.com/jp/news/2020/ 02/7-1,html)

メルコインベストメンツ株式会社と共同で、リスクの少ない株式ポートフォリオの生成に成功した. 従来,数百銘柄の最適ポートフォリオを組合せ最適化計算で求めることは、膨大な計算量のため不可能であった. 今回,デジタルアニーラで最適化計算が10分程度で可能となり、実際の資産運用業務に活用することができるようになった.

・事例 2:物流(https://pr.fujitsu.com/jp/news/2020/ 09/10-1.html)

(株)トヨタシステムズの自動車製造に必要な部品の物流ネットワークを最適化する実証を行った.数百を超える仕入れ先から部品を仕入れ,数か所の中継倉庫を通り,数十の工場へ配送する300万以上の候補ルートから最適解を探索する問題をデジタルアニーラで計算した.従来30人で2か月かけて計画立案していた問題を,僅か30分で解くことに成功した.

・事例 3:創薬(https://pr.fujitsu.com/jp/news/2020/ 10/13.html)

ペプチドリーム株式会社と共同で、環状ペプチドによる中分子創薬において、デジタルアニーラと HPC (High Performance Computing) を用い、従来、現実的な時間ではできなかった創薬の候補化合物となる環状ペプチドの安定構造探索を 12 時間以内に高精度で行うことに成功した。

以上のように、受賞者らは新しい計算機アーキテクチャを創出し、それを実問題に適用して各種事業に貢献しており、その成果は業績賞にふさわしいものである.

#### 文献

- (1) S. Matsubara, M. Takatsu, T. Miyazawa, T. Shibasaki, Y. Watanabe, K. Takemoto, and H. Tamura, "Digital annealer for high-speed solving of combinatorial optimization problems and its applications," The 25th Asia and South Pacific Design Automation Conference, no. 9C-2, pp. 667-672, Beijing, China, Jan. 2020.

- (2) S, Matsubara, H. Tamura, M. Takatsu, D. Yoo, B. Vatankhahghadim, H. Yamasaki, T. Miyazawa, S. Tsukamoto, Y. Watanabe, K. Takemoto, and A. Sheikholeslami, "Ising-model optimizer with parallel-trial bit sieve engine," Conference on Complex, Intelligent, and Software Intensive Systems (CISIS) 2017, pp. 432-438, 2017.

- (3) H. Tamura, S. Matsubara, T. Ahmed, M. Takatsu, D. Yoo, B. Vatankhahghadim, H. Yamasaki, T. Miyazawa, S. Tsukamoto, Y. Watanabe, K. Takemoto, Y. Koyanagi, and A. Sheikholeslami, "An architecture for parallel-trial hardware accelerator for ising-model MCMC simulations," Adiabatic Quantum Computing Conference 2017, 2017.

- (4) H. Tamura, T. Miyazawa, J. Koyama, N. Yoneoka, S. Matsubara, M. Takatsu, Y. Liu, T. Shibasaki, S. Tsukamoto, Y. Watanabe, K. Takemoto, Y. Koyanagi, T. Horie, T. Urushidani, T. Ozaki, M. Sumida, A. Sheikholeslami, and K. Hukushima, "Digital annealer: An accelerator for Markov-chain Monte Carlo stochastic search with multi-replica processing," Adiabatic Quantum Computing Conference 2018, 2018.

- (5) T. Miyazawa, N. Yoneoka, S. Matsubara, Y. Liu, T. Shibasaki, K. Takemoto, Y. Koyanagi, H. Tamura, T. Ozaki, T. Urushidani, M. Aramon, and H.G. Katzgraber, "Stochastic search using digital annealer technology," Adiabatic Quantum Computing Conference 2018, 2018.

## 東京大学大規模集積システム設計教育センター (VDEC) における集積回路設計教育研究 に対する多大な貢献

受賞者 池田 誠

大規模集積システム設計教育センター(VDEC)は1996年に全国共同利用施設として東京大学に発足以来、日本の大学における集積回路の設計教育・研究に多大な貢献をもたらしてきた、VDEC 開設以前の日本の集積回路設計は設計に必要な EDA(Electronic Design Automation)ツールの調達や試作の契約を個々の研究者が行わなければならず、その金銭コストと人的コストは甚大で、結果として集積回路設計研究に携わる大学の研究者は僅少であった、VDEC は EDA ツールの一括契約と

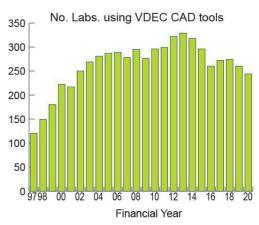

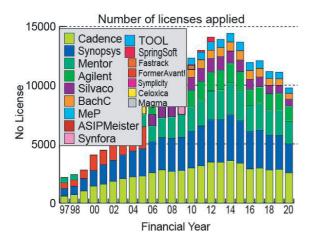

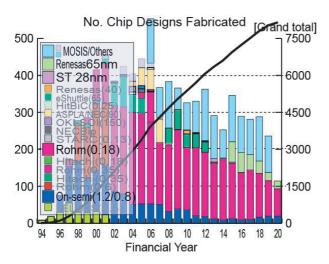

そのライセンスの高専・大学への供給,設計データを一括して集めて安価に試作を行うシャトルサービスの提供を行い,教員並びに学生の負担を大きく低減し,日本のアカデミック分野の裾野の拡大に大きな役割を担った.EDAツールのライセンス数は開設当初は2,000程度であったが,2005年には1万を超えた(図1,2).試作チップ数も開設年度は100にも満たなかったが,2006年には500を超えた.なお,開設前はゼロに近い年間一桁であっ

図1 EDA ツールの利用研究室数

図2 EDA ツールの利用ライセンス数

図3 チップ試作の設計数

た. 試作可能なプロセスは開設当初から現在も続いている非常に安価な  $1.2/0.8~\mu m$  プロセスに加え、 $0.6~\mu m$ ,  $0.5~\mu m$ ,  $0.35~\mu m$ ,  $0.18~\mu m$ ,  $0.15~\mu m$ , 90~n m,  $65~n m^{(1)}$ , 45~n m, 28~n m とプロセスルールの微細化とともに試作プロセスも変遷し続け VDEC 発足来  $24~\pi l$  で 8,100~l 品種を超える試作が行われている(図 3).

EDA ツールの使用方法の講習会である CAD 講習会を 1997 年から、社会人と学生向けのハンズオンチュートリアル的なリフレッシュ教育を 1998 年から開催し、共に現在に至るまでアップデートを続けながら連続して開催している <sup>(2)</sup>. 更に、若手研究者と学生の情報交換の

場として 1997 年に VDEC を支える若手の会を開催し、翌年の 1998 年からデザイナーズフォーラムと改称し 24 回で 1,000 名を超える参加者となり、情報交換のみならず学生が設計した回路の表彰の場も設け、学生の研究意欲向上にもつながっている。結果としてこれまで 24 年間で VDEC 活動に関連した論文発表件数は 1 万 6,000件を超えるに至っている。

受賞者は大規模集積システム設計教育研究センター (VDEC) における集積回路設計教育(3)~(7)研究活動(8),(9) を通した人材育成に尽力され,多大な成果を上げた.受 賞者(浅田)は、VDEC設立時のセンター組織の基本 設計と活動基本方針を作成し、2000年からその定年退 職の 2018 年まで 18 年にわたり VDEC センター長を務 め、その運営に多大な貢献をした、受賞者(池田)は VDEC 設立と同時に助手として採用され、助教授、准 教授を経て 2013 年から教授を務め、VDEC 全般の業務 に深く携わった. また VDEC は 2019 年に東京大学シス テムデザイン研究センター (d.lab) の発足に伴う改組 によりその一部門として再スタートを切った. 受賞者 (池田) は改組後に d.lab の基盤設計研究部門の部門長 として引き続き、EDA ライセンスの供給と試作データ の取りまとめという旧 VDEC の2大事業の取りまとめ を行っている。以上のとおり、VDEC における受賞者 らの20年以上にもわたる貢献は日本の集積回路分野の 発展に欠かせぬものであり、その献身的な活動は業績賞 に該当する極めて大きな業績であると考えられる.

#### 文献

- (1) 池田 誠, NANO-CHIPS 2030, Springer, ドイツ, 2020.

- (2) 池田 誠,越智裕之,小林和淑,ディジタル集積回路の設計と 試作,浅田邦博(監修),培風館,東京,2000.

- (3) 浅田邦博,アナログ電子回路―VLSI工学へのアプローチ,昭晃 堂,東京,1998.

- (4) システム LSI 設計自動化技術の基礎―パブリックドメインツールの利用法,浅田邦博(監修),培風館,東京,2005.

- (5) アナログ RF CMOS 集積回路設計 基礎編/応用編, 浅田邦博 (編集), 培風館, 東京, 2010/2011.

- (6) 浅田邦博,集積回路設計,電子情報通信レクチャーシリーズ C-13,電子情報通信学会(編),コロナ社,東京,2015.

- (7) 池田 誠, MOS による電子回路基礎, 数理工学社, 東京, 2011.

- (8) はかる×わかる半導体 入門編, 浅田邦博(監修), 日経 BP コンサルティング, 東京, 2013.

- (9) はかる×わかる半導体 応用編,浅田邦博(監修),日経 BP コン サルティング,東京, 2019.