# オンチップ伝送線路配線の期待と課題

On-chip Transmission Line Interconnect

益 一哉

Si CMOS の性能向上は"微細化"に尽きるが、現在、多くの問題や課題が立ちはだかっている。本稿では、グローバル配線を中心に配線遅延についての問題、オンチップ伝送線路配線技術と更に将来に向けての展望について紹介する。 キーワード:微細化、CMOS 集積回路、伝送線路

#### 1. はじめに

Si CMOS (Complementary MOS) 集積回路はスケーリング則を指導原理として微細化してきた. 「スケーリング則」の本質とは、技術的側面としての高速、低消費電力、高集積という「性能向上」とチップ面積縮小と相まって経済的側面としての「低コスト化」を両立してきたことである. ところが最小加工寸法が 100nm を切るようになり、材料、デバイス、プロセス、インテグレーション、回路、設計、アーキテクチャ、システム化、製造コストなどすべての側面において、従来手法の延長だけでは限界が見えつつあり、加工寸法を微細化しただけでは、性能向上もしない、コストも低減しないという非常に厳しい状況にある. 高性能と経済性の両立を目指す "真のスケーリング:True Scaling"をあらゆる手段と知恵を結集して追求する必要がある.

古くから配線遅延が性能を律するといわれてきた.本稿では、配線遅延にまつわる課題と筆者のグループで開発している伝送線路配線技術の最近の成果、更に今後の課題について述べる.

#### 2. 配線運延

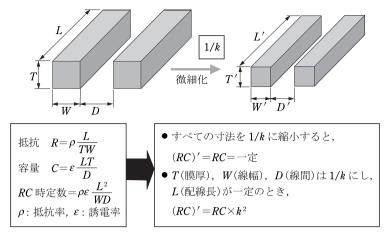

図1に配線の RC 時定数を示す. 回路の遅延は, 近似的にはデバイスのスイッチング時間と配線遅延の和で

ある. 配線長まで含めて寸法を微細化したとき, 配線の RC 遅延時間はそもそも改善しない(1). デバイスのスイッチング時間が主である場合は, 配線遅延は考慮する必要はなかった. 現実の集積回路では, 加工寸法が微細化した際にチップサイズは余り減少せず(あるいは大きくなっている), チップを横断するような長距離配線(グローバル配線と呼ばれる)の配線遅延がチップ性能そのものを律速するようになってきた.

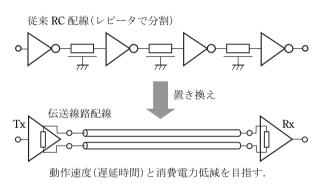

一般に長距離配線は、図 2 に示すように分割してレピータ  $(\pi, \pi)$  を挿入してトータルの遅延時間を改善してきた。しかし、レピータ挿入による消費電力増加やレピータ面積増加が問題となってきている。そもそも電気配線は周波数が高くなって信号波長が線路長に対して無視できなくなると信号を電磁波と考えた伝送線路的な発想をする必要がある。おおよそ、信号の基本周波数に対応する波長を入とすると線路長 L が  $\lambda/40$  より長くなれば伝送線路として考える (2) 。 筆者の研究グループでは、図 2 に示すように従来レピータで分割していた配線を伝送線路に置き換える技術の開発を行っている。伝送線路配線の特徴は、配線遅延はほぼ電磁波の場合と等しく、また差動線路を利用することで低振幅でも信頼度の高い信号伝送が可能である点にある。

# 3. 伝送線路配線

伝送線路配線を実現するためには,線路構造と駆動・ 受動回路の開発を行う必要がある.

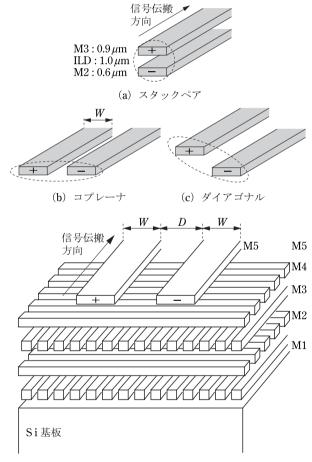

まず、線路についてであるが、Si CMOS 多層配線中に構成可能な差動線路構造として、図 3 に示す構造が考

益 一哉 正員 東京工業大学統合研究院

E-mail masu@ieee.org

Kazuya MASU, Member (Integrated Research Institute, Tokyo Institute of Technology, Yokohama-shi, 226-8503 Japan).

電子情報通信学会誌 Vol.91 No.3 pp.170-175 2008 年 3 月

図1 配線遅延

図2 従来 RC 配線と伝送線路配線

えられる。線路のインピーダンスは任意に選択することが可能である。抵抗損の影響を避けるためには特性インピーダンスを大きくした方がよい。一般にクロストーク (用語) ノイズ低減のためには特性インピーダンスは小さい方がよい。現在のところ,寸法的に多層配線に組み込みやすいことから差動インピーダンスで  $100\Omega$  の線路としている。設計の立場から考慮すべきことは,新規プロセスや材料を開発するという立場ではなく,構築された条件(材料,寸法)のもとで最適の設計や方策を模索することである。図 3 (a) のスタックペア構造は,絶縁膜

#### ■ 用 語 解 説

レピータ 語源としては中継器.集積回路におけるミリメートル以上の長距離配線は一般に分割してインバータ回路を挿入して,全体の遅延時間を改善している.挿入したインバータ回路をレピータという.

**クロストーク** 複数の信号線があったときに,一方の信号線から他方の信号線への信号の重畳.

バス コンピュータの内外や各回路間がデータを交換するための共通の信号経路.

ビア 集積回路の多層配線層構造において,上下配線間 の金属接続孔のこと.

マルチコア 二つ以上のプロセッサコアを一つのチップ やパッケージに集積したマイクロプロセッサの通称.

(d) 多層配線構造における差動伝送線路構造

図3 差動伝送線路構造

厚を設計者が任意に変化させることができず、 $100\Omega$ 線路形成のためには線路幅が $1\mu$ m以下と小さくなりすぎ、線路自身の抵抗損のため伝送線路を構成できない。コプレーナ型、ダイアゴナル型、共に線路間隔を調整することで所望の特性インピーダンスを持つ線路を形成することができる。

多層配線中の伝送線路はバス<sup>(用語)</sup>などへ利用すること

表 1 オンチップ伝送線路配線の特性(6)~(10)

|      |                                                                          | 技術世代<br>(nm) | データ速度<br>(Gbit/s) | 消費電力<br>(mW) | 遅延時間<br>(s/cm)     | エネルギー<br>(J/bit) | 発表年      |

|------|--------------------------------------------------------------------------|--------------|-------------------|--------------|--------------------|------------------|----------|

| 目標特性 |                                                                          | 180          | 2                 | 9            | 180                | 4.5              |          |

|      |                                                                          | 90           | 10                | 5            | 110                | 0.5              |          |

|      |                                                                          | 45           | 30                | <5           | 70                 | < 0.17           |          |

| 実測特性 | CML $(L=2\text{mm})^{(a)}$                                               | 180          | 4                 | 54.4         | 320 <sup>(b)</sup> | 13.6             | 2005(6)  |

|      | $CML$ (低電源電圧タイプ, $V_{\mathrm{DD}}{=}1\mathrm{V}$ )( $L{=}2\mathrm{mm}$ ) | 180          | 3                 | 8.9          | 339 <sup>(b)</sup> | 2.97             | 2005 (7) |

|      | 非対称タイプ( <i>L</i> =3mm)                                                   | 90           | 5                 | 6.5          | 187 <sup>(b)</sup> | 1.3              | 2006(8)  |

|      | LVDS, イコライジング 90nm<br>( <i>L</i> =5mm)                                   | 90           | 11                | 2.7          | 207 <sup>(b)</sup> | 0.25             | 2007 (9) |

|      | Tx/Rx 一体型, マルチドロップ ( <i>L</i> =5mm)                                      | 90           | 8                 | 2.4          | 184 <sup>(b)</sup> | 0.3              | 2007(10) |

- (a) Lは、試作回路の線路長である.

- (b) 実測遅延時間に、線路のみの遅延時間 (0.67ps/mm) を加算して1cm 当りに換算している.

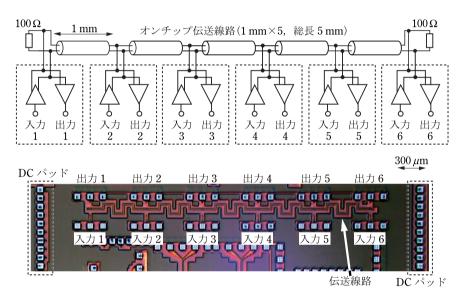

図 4 伝送線路配線<sup>(10)</sup> 90nm CMOS プロセスを利用. この配線では 1mm ごとに入力出力ポートがあり, 双方向でデータ伝送可能である.

から、多数本併走する必要がある。このようなときに隣接配線からのクロストーク低減が重要である。図3(c)のダイアゴナル構造では配線ピッチを小さくすることができるので、多層配線に利用するときには有用な構造である<sup>(2)</sup>.

1 cm 程度の伝送線路配線では,配線そのものの抵抗損の影響を少なくするために線幅はおおよそ  $4 \mu \text{m}$  程度必要である.実際の線路では曲げやビア (用語)が存在する.ビアや曲げは一か所当り,損失としては 0.1 dB 以下であるので (2) ,10 Gbit/s 程度までの信号伝送では大きな問題にならないが,数十 (2) Gbit/s 以上の信号においては検討が必要である.

単純な線路設計では配線間隔だけがパラメータになるが、実際のLSI配線では、図3に示すように下層配線やダミーメタルが存在するため、伝搬定数や伝搬損が変化する。これら多層配線構造を考慮した配線モデリングが

行われている<sup>(3),(4)</sup>. 別の側面として, ダマシンプロセスの要求からダミーメタルを必ず挿入する必要があり, 信号線路の周囲の構造が周期的に見えるようになってくる. 信号線路の周囲が周期的構造になったときの配線モデリングは長距離配線だけではなく短距離, 中距離配線においても重要な課題である<sup>(5)</sup>.

これまでに幾つかの線路と駆動・受動回路の開発を 行ってきた。表 $1^{(6)^{\sim}(10)}$ に目標特性とこれまでに報告し た特性を示す。

図4は伝送線路配線の一例を示している<sup>(10)</sup>. 総長5mmの伝送線路に1mmごとに入出力回路を設けている。各ポートでは信号の入出力を切り換えることでバスへの利用が可能である。この回路で双方向に8Gbit/s以上の信号伝送を行うことができる。

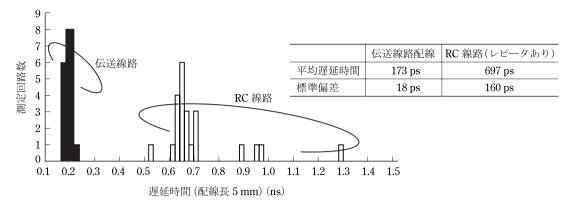

図5は,配線長5mmの単純な一方向伝送線路の遅延時間ばらつきを示している.この線路では10Gbit/s以

図 5 伝送線路配線の遅延時間ばらつき<sup>(9)</sup> 90nm CMOS プロセス利用. 配線長は 5mm.

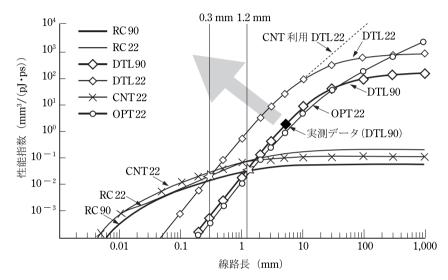

図6 種々の配線の性能指数 (FoM) RC: 従来 RC 配線, CNT: カーボンナノチューブを利用した配線。 DTL: 差動伝送線路, OPT: 光配線.数値は当該配線を駆動する回路の技術世代,例えば RC90 とは, 90nm CMOS プロセスを利用した RC 線路のこと.

上の信号伝送を行うことができる。伝送線路配線の場合は、駆動回路と受動回路の間に 5mm の伝送線路が存在する。RC線路では線路をレピータで分割し、配線の総長は 5mm である。絶縁膜の比誘電率が約 4 であるとき、Time-of-Flight は約 33ps である。伝送線路配線の場合、駆動・受動回路で約 100 数十 ps の遅延がある。しかしながら、レピータを挿入した従来型の RC線路に比較して、遅延時間は小さい。重要な点は、遅延時間のばらつきが小さいことである。従来 RC 配線では、レピータ回路の遅延ばらつきが大きく、結果としての線路全体の遅延時間ばらつきが大きくなってしまっている。遅延時間ばらつきが小さいことは伝送線路配線の大きな特徴である。

LSI のグローバル配線として、伝送線路配線はプロセスへ負担がないという大きな特徴を持っている。これに対して、新規材料や新規方式の導入の検討も行われている。例えばカーボンナノチューブ(CNT)を利用したり、光配線(11)を利用する方法である。これら種々の配線の

性能を同じ土俵で評価する必要がある。式(1)の性能指数(FoM:Figure of Merit)を新規に定義し各種配線技術の性能を比較した $^{(12)}$ .

$$FoM = L^3/E \cdot D \tag{1}$$

ここで,L は配線長,E は 1 bit 当りのエネルギー,D は遅延時間である.1 bit 伝送するために必要なエネルギーが小さくかつ遅延時間の短い配線の F oM は大きくなる

図6に各種配線技術のFoMを示す. CNT 配線は従来型のRC 配線をCNT に置き換えた構造を想定している. そのため、線間容量は存在するので配線抵抗低減の効果しかないためFoMの大きな改善はない. FoMの観点からは90nm世代では1.3mm, 22nm世代では0.3mmより長い配線では伝送線路配線の性能指数が大きな値を有している. ただし、伝送線路配線であっても長さ数cmのオーダとなるとレピータを挿入する必要が

あるため、光配線の方が有利になる.

この比較では、線路そのものや回路の専有面積の効果が含まれていない。面積を考慮した性能比較が今後必要である。

# 4. 今後の課題

これからの集積回路開発において、SoC (System on Chip) 的発想ばかりではなく、SiP (System in Package) や三次元実装技術の利用により LSI の性能向上を目指す幾つかの方法がある。しかし、チップそのものの性能向上は徹底的に検討する必要がある。

本稿で紹介させて頂いたようにグローバル配線では伝送線路配線を利用する有用性の見通しが立ってきた.クロック周波数の向上とチップ面積の増加により、チップ全体の同期をとることが難しくなってきたので、プロセッサにせよ、SoCにせよ、マルチコア(用語)的な発想が必要になる.ネットワークオンチップもその流れに沿うと考えることができる.まずは、コア間に伝送線路配線を利用する手法や設計手法を開拓することが次のステップと考えている.

マルチコアやネットワークオンチップ的な手法における配線遅延の課題を指摘させて頂く.

例えば、既にある回路ブロックを単純に次世代プロセスを利用して、すなわち図1のkでスケーリングした場合、配線遅延は改善しない。その回路ブロックあるいはそれがコアであったとすると、動作周波数を上げるためにレピータを挿入すると面積が縮小しない、あるいは最悪のシナリオでは技術世代が進んでも回路ブロックやコア面積が大きくなってしまうこともある。すなわち、経済的スケーリングはこんな単純なところも破たんしかかっている $^{(13),(14)}$ .

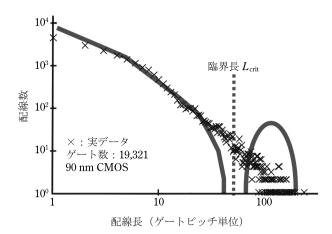

これまでの LSI の配線分布は統計的に表現することが できる(15),(16). 将来の LSI の必要配線資源の予測や性能 予測に利用できる. 図7に配線長分布の一例を示す. 意 識的に同長でレピータを挿入しないとロジック回路の配 線長分布はおおむねこのような形になる. 伝送線路配線 技術の開発を始めたころ、長距離配線をすべて伝送線路 にするとの発想に立つと配線長分布は図中に示すような 分割形に意識的にするような設計が必要であると指摘し  $c^{(17)}$ . 臨界長  $L_{crit}$  は、世代ごとに要求される伝送速度 で決まると考えた. ネットワークオンチップやマルチコ アを構成する回路ブロックの一辺の寸法を単純に $L_{crit}$ 以下とし、コア間は伝送線路で接続するという発想であ る.しかし、上記に指摘したように、ネットワークオン チップやマルチコアを構成する回路ブロックが技術世代 が進んでも性能向上とチップ縮小(低コスト化)ができ ないとなると、単純に $L_{crit}$ を決めればよいということ にはならない.

図 7 配線長分布 分割形配線長分布の提案. ゲートピッチを利用すると, ゲート数の平方根がほぼチップ一辺の長さである.

まずは、コアや回路ブロックは技術世代ごとにスケー リング(ここでのスケーリングとは性能と面積が共にス ケーリングされること)できるのかできないのかを定量 的に示すことが出発点である. コスト増覚悟で多層配線 層数を増やしたとしても, ビア数激増による抵抗増大で 恐らく遅延時間は改善しないと予想される. 今一度配線 長分布に戻ってみる. 配線長分布は長い世代にわたって このような分布になっており、将来世代の分布も予想で きる、配線本数の増大と遅延が問題であるならば、配線 本数を減らすしかない. システムアーキテクチャレベル での配線本数低減の検討が必要である。一方で、同路設 計者としては、信号の多重化を今一度検討する必要があ る. 信号の多重化は信号伝送の品質を低下させることは 必至であるが、配線本数を減らすというより大きな目標 に向かって, 多値伝送や信号伝送に変調をかけるといっ た検討をしなければならないと考えている.

### 5. ま と め

本稿では、オンチップ信号伝送の最近の研究と今後の 課題について述べた.

マルチコアやネットワークオンチップ的な発想でのSoCの性能向上のためには、回路レベルでは配線本数低減のために信号多重伝送の再考が必要であるとの指摘を行った. 恐らく一つの方向であると考えている. しかし、True Scaling を標榜し、45nm 以降の技術開発を目指すには、研究のための研究にならないように、あるいは開発しました、作りましただけにならないように、マルチコアやネットワークオンチップといった LSI が、いつの技術世代で、何に利用されるのか、といった研究目標の明確化をマーケティング的な発想をもって遂行したいと考えている.

謝辞 本研究の一部は,文科省科学研究費補助金(特定領域研究),日本学術振興会科学研究費補助金,半導

体理工学研究センター(STARC)、NEDO/MIRAI 先導研究の支援を受けました。また、回路試作に関しては東京大学 VDEC(VLSI 設計・教育センター)の支援を受けました。関係各位に感謝致します。本稿で紹介した研究は岡田健一准教授、伊藤浩之助教、天川修平助教、並びに多くの大学院生と行ったものであり、深く感謝致します。また、STRJ 設計 TF にて多くの議論をして頂いている石橋孝一郎氏、浅田善己氏並びに委員各位に感謝致します。研究におけるマーケティングの重要性については、柏木正弘氏(熊本県産業技術センター)並びに前川耕司氏 (PDF Solutions) に御議論、御教示頂きました。深く感謝致します。

#### 文 献

- H.B. Bakoglu, Circuits, Interconnections and Packaging for VLSI, Addison-Wesley, 1990. (訳本: VLSI システム設計―回 路と実装の基礎, 丸善, 1995.)

- (2) K. Masu, K. Okada, and H. Ito, "RF passive components using metal line on Si CMOS," IEICE Trans. Electron., vol.E89-C, no.6, pp.681-691, June 2006.

- (3) H. Ito, K. Okada, and K. Masu, "A loss optimization method using WD product for on-chip differential transmission line design," IEEE Workshop on Signal Propagation on Interconnects (SPI), pp.217-220, Berlin-Mitte, Germany, May 2006.

- (4) A. Tsuchiya and H. Onodera, "Measurement of interconnect loss due to dummy fills," Proceedings of 11th IEEE Workshop on Signal Propagation on Interconnects, pp.241-244, May 2007.

- (5) S. Amakawa, H. Ito, and K. Masu, "Signal transmission through interconnects with repetitive loads," Advanced Metallization Conference (AMC), pp.173-174, Albany, New York, Oct., 2007, and Advanced Metallization Conference, Asian Session (ADMETA), pp.94-95, Tokyo, Oct. 2007.

- (6) H. Ito, H. Sugita, K. Okada, and K. Masu, "4 Gbps on-chip interconnection using differential transmission line," IEEE Asian Solid-State Circuits Conference, pp.417-420, Nov. 2005.

- (7) H. Ito, K. Okada, and K. Masu, "Development of differential transmission line interconnect IP for high-speed global interconnect," Circuit Exhibition of European Solid-State Device Research Conference and European Solid-State Circuits Conference, Poster 26, Sept. 2005.

- (8) T. Ishii, H. Ito, M. Kimura, K. Okada, and K. Masu, "A 6.5-mW 5-Gbps on-chip differential transmission line interconnect with a low-latency asymmetric Tx in a 180nm CMOS technology," IEEE Asian Solid-State Circuits Conference (A-SSCC), pp.131-134, Hangzhou, China, Nov. 2006.

- (9) H. Ito, J. Seita, T. Ishii, H. Sugita, K. Okada, and K. Masu, "A low-latency and high-power-efficient on-chip LVDS transmission line interconnect for a RC interconnect alternative," IEEE International Interconnect Technology Conference (IITC), pp.193-195, San Francisco, June 2007.

- (10) H. Ito, M. Kimura, K. Okada, and K. Masu, "A 8-Gbps low-latency multi-drop on-chip transmission line interconnect with 1.2-mW two-way transceivers," IEEE Symposium on VLSI Circuits, pp.136-137, Kyoto, June 2007.

- (11) K. Ohashi, J. Fujikata, M. Nakada, T. Ishi, K. Nishi, H. Yamada, M. Fukaishi, M. Mizuno, K. Nose, I. Ogura, Y. Urino, and T. Baba, "Optical interconnect technologies for high-speed VLSI chips using silicon nano-photonics," IEEE International Solid State Circuits Conference, pp.1686-1695, Feb. 2006.

- (12) K. Okada, H. Ito, and K. Masu, "On-chip differential transmission line (DTL) interconnect for 22nm technology," Advanced Metallization Conference (AMC), pp.2-3, San Diego, CA, Oct. 2006, and Advanced Metallization Conference, Asian Session (ADMETA), pp.124-125, Tokyo, Sept. 2006.

- (13) 石橋孝一郎(半導体ロードマップ委員会(STRJ),設計タスクフォース),低電力SOCのロードマップ一配線分布・抵抗の予測とSOC性能に及ぼす影響,STRJワークショップ,2007年3月9日,http://strj-jeita.elisasp.net/strj\_workshop\_06nedo\_0309.cfm

- (14) P. Saxena, N. Menezes, P. Cocchini, and D.A. Kirkpatrick, "Repeater scaling and its impact on CAD," IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol.23, no.4, pp.451-463, 2004.

- (15) S. Amakawa, T. Uezono, T. Sato, K. Okada, and K. Masu, "Adaptable wire-length distribution with tunable occupation probability," International Workshop on System Level Interconnect Prediction (SLIP), pp.1-8, Austin, Texas, March 2007.

- (16) J.A. Davis, V.K. De, and J.D. Meindl, "A stochastic wire-length distribution for gigascale integration (GSI)-part I: Derivation and validation," IEEE Trans. Electron Devices, vol.45, no.3, pp.580-589, March 1998.

- (17) 益 一哉,坪内和夫,高速信号伝送技術,日本学術振興会第 165/151委員会資料,pp.48-55,July 2000.

$(平成 \, 19 \, \mp \, 11 \, \hbox{$\it |$|} \, 14 \, \hbox{$\it |$|} \, {\rm \Box} \, {\rm$

# は 一哉 (正員)

昭50神戸高専・電気卒、昭52東工大・工・電子物理卒、昭57同大学院博士課程了、工博、同年東北大電気通信研究所助手、平5同助教授、平13東工大精密工学研究所教授、平17同大学統合研究院教授、現在に至る、高速信号伝送技術、Si RF CMOS 回路技術、統計的集積回路性能評価・予測の研究に従事、IEEE、応用物理学会、電気学会、エレクトロニクス実装学会各合目