|

■3. システムLSIの技術課題

次に,システムLSIが直面している技術課題とその解決策について簡単に触れる.

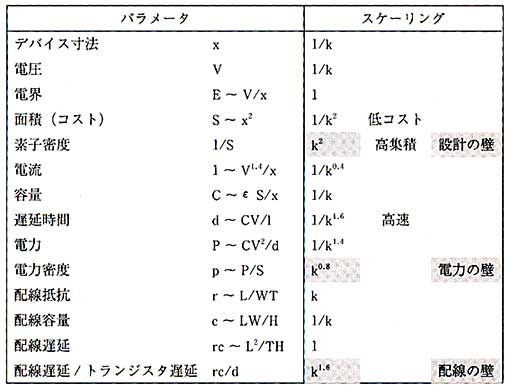

デバイスをスケーリングすると,性能は上がりコストは下がると述べたが,中には悪くなるものもある.デバイスのスケーリング則を表2に示す.この表から次の三つの課題があることが分かる.一つは,低電力化.表1に示したように2015年には,540W,1.8kAのチップが出現する.微細化するほど必然的に増大する電力をいかにして削減するかが緊急の課題である.二つ目は,配線技術.2015年には,配線層数は十層以上になり,製造コストが高くなる.また,チップの端から端まで信号が伝搬する時間は,クロック周期の10倍以上になると予想される.性能,コスト,製造時間,共にトランジスタよりも配線が支配的になる.三つ目は,設計の複雑さ.現在より2けた多い100億のトランジスタを集積するためには,設計効率も同様に改善されなければならない.各課題について,最近の研究成果を簡単に紹介しよう.詳しくは,“3-1 システムLSIを支えるデバイス,プロセス技術”(池田修二氏,ほか)と“3-2 デシミクロンCMOSシステムLSIの低消費電力技術とチップアーキテクチャ”(水野正之,相本代志治両氏)を見て頂きたい.

表2 スケーリング則に見る微細化の課題

例えば1/2にスケーリングすると,回路は3倍速くなり,チップ面積は1/4に小さくなる.

一方,電力密度は1.5倍に増え,配線遅延はスイッチング遅延に比べて3倍遅くなり,

素子密度は4倍になって設計が複雑になる.

3.1 電力の壁

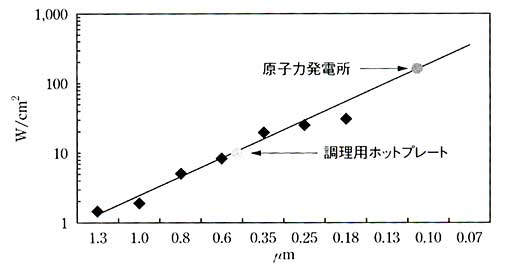

表2から分かるように,スケーリングするほど電力密度は増大する.図8にこれまでの電力密度の推移を示す.既に調理用ホットプレートの3倍熱い.単純に外挿すると,2005年の0.1pm時代には,原子力発電所の発電電力密度に匹敵する.そうなると,世界中で動いているチップの総面積に相当する原子力発電所を稼動させなければ電力需要を賄えないことになり,地球規模のエネルギー問題を生じる.実際には,これほど急速に電力密度は増大しないだろう.以前は電源電圧が余り下がらず,電力密度が急増した.最近では,電源電圧が下がり,表2に示すような電界一定のスケーリングに近いからである.表2から,チップの電力は3年で40%ずつ増大すると予想される.それでも2015年には540Wにもなってしまう.

図8 電力密度の推移

今日のLSIは既に調理用ホットプレートの3倍熱い.

単純に外挿すると,2005年の0.1pm時代には,原子力発電所の発電電力密度に匹敵する.

そうなると,世界中で使われているチップの総面積に相当する原子力発電所を稼働させなければ

電力需要をまかなえないことになり,地球規模のエネルギー問題を生じる.

実際には,電源電圧の低下に伴い,電力密度の増加は,もう少し緩やかなペースになるだろう.

対策はどうすればいいのだろうか?CMOSの電力は,P =pfCV2( pはスイッチング確率,fは動作周波数,Cは容量,Vは電圧)で与えられるので,これらのパラメータを小さくすることが電力削減策になる.そのためには,技術の総合力が必要になる.

まずアーキテクチャから考えよう.商品企画の段階では,機能を顧客の求める必要最小限に絞ることが肝要である.また,求められる性能は状況ごとに異なることが多いので,常に最高性能を出す設計よりも,要求に応じて性能を変化させることができる設計が,これからは重要になる.また,外部メモリのアクセスには大きなエネルギーが必要なので,外部メモリへのアクセスはできるだけ少なくしたい.あるいは,取り扱う信号の性質をよく知り,データ遷移確率が低くなるデータ表現を与えることも有効である.マイクロプロセッサでは,これまで性能だけを追究してきたが,これからは性能と電力の両方を考慮したマイクロアーキテクチャが求められるだろう.例えば一般ロジックを増やしてチップサイズを2倍にしても性能は1.4倍にしか増えない(Pollack's

Rule).一方,通信やヒューマンインタフェースへの応用では,並列性を生かして,特殊なハードウェアを追加することが,性能改善に効率的である.また,ロジックに比べてメモリは1けた電力密度が低い.キャッシュメモリを2倍にすると,キャッシュによる性能改善分は1.4倍になるといわれている.チップサイズは今後増大しても,ロジックの占める面積は縮小するかもしれない.

ロジックのレベルでは,年々増加するクロックの電力削減が重要である.細めにクロックを止めるとともに,データが変化しないときは動作しないフリップフロップが非常に有効である.

回路のレベルでは,低電圧化が最も有効である.電源電圧(VDD )を下げると回路動作は遅くなる.それでもチップの性能を損なわないようにするには,三つの方法がある.一つは,並列・パイプライン処理で性能を上げることである.ディジタル信号処理では有効であるが,チップ面積が大きくなるのがペナルティである.二つ目の方法は,回路遅延の増大を招かないようにトランジスタのしきい値電圧(VTH

)を低くすることである.VTH を下げるとトランジスタの漏れ電流が増えるので,幾つかの対策が研究されている.待機時は電源を切るのが一つの方法である.しかし動作時には電源を切れないので,動作時の漏れ電流は別の解決が求められる.VTH

を下げると回路動作の電力は減るが,漏れ電流による電力は増える.両者を合わせた全電力が最小になるのは,チップの漏れ電流が電源電流の数十%程度になるようにVTH

を下げたときである.必要な性能は刻刻と変るので,VDD とVTH

を時間的に変化させる技術がいろいろと研究されている.三つ目の方法は,チップの中で高速に動作させたい回路には高いVDD

と低いVTH を使い,ゆっくりでも構わない回路には低いVDD

と高いVTH を使う方法である.すなわち,多電源,多しきい値電圧を使い分けることである.これは,言い換えれば,余った時間を電力削減に還元していることになる.このように,VDD

とVTH は,設計者が最適化すべき重要な設計パラメータになってきた.第二の方法ではそれらを時間的に最適化し,第三の方法では空間的に最適化することになる.一方,電源電圧の低下にもかかわらず電力は増大するので,電源電流は急増する.電源の分配,電源ノイズの対策などがますます難しい問題になる.

デバイスのレベルでは,低電圧で高性能なSOI(シリコンオンインシュレータ)が注目されている.また,DRAM混載技術は,メモリアクセスのための電力を大幅に削減できるので,低電力なシステムに有効である.プロセスのレベルでは,低誘電率配線絶縁材料や空中配線技術の開発が期待される.また,CADは,電力を正しく評価して性能とのトレードオフを適切に取る上で,今後も重要な役割を担う.

3.2 配線の壁

先に述べたように,配線がチップのコスト,製造時間,動作速度,消費電力を決めるようになるだろう.したがって配線遅延や配線容量を減らす技術,あるいは配線数や配線層数を減らす技術が重要になる.

かつてはボード上で実現していたシステムが,一つのチップに集積されるようになってきた.これからは,チップの外で使われていた通信技術がチップの中に入ってくるだろう.また,チップ内部でもモジュール間の通信にはコストがかかるということをハードウェア及びソフトウェア設計の各レベルで十分に認識しなければならない.更に,アーキテクチャ設計も,演算効率の追究から通信効率の追究へと重点が移るだろう.システムを階層にして,頻繁な通信は小グループ内に収まるように工夫することが必要になる.

チップを上下に重ねて高密度に上下で配線できれば,問題は一気に解決する.チップサイズも年々小さくできる.しかし,良品チップをどのように選別テストするかなどの課題は多い.

3.3 複雑さの壁

LSIの集積度が年率59%で増えるのに対して,設計可能な回路規模は年率21%でしか増えない.10年後には,両者におよそ15倍のかい離を生ずる.理工学では,抽象化を積み上げることで思考やデザインの範囲を拡大するのが一般的手法である.集積回路の設計でも,より上流の設計の自動化を果たすことで,設計生産性を向上してきた.1970年代はポリゴン(トランジスタ),1980年代はレイアウト(セル),1990年代は論理(RTL:Register

Transfer Level)のレベルであった.これからは,機能(C言語),仕様(IP:Intellectual Property)へと抽象度が更に高くなっていくだろう.

一方,LSIの設計コストやマスクコストは今後増大するので,標準ハードウェアを使ってソフトウェアでカスタマイズするアプローチが増えるかもしれない.しかし,専用ハードに比べてソフトウェア処理は,より大きな電力を消費する点に気をつけなければならない.開発期間,経済性と性能のトレードオフがハードウェアとソフトウェアの分担を決める.いずれにしても,LSI設計資産やソフトウェアの再利用がこれからの設計自動化の課題である.

|