|

■ 2. Jisso技術を電気的にとらえる

Jisso技術は日本語の「実装」技術の言葉から想像できるようにその技術範囲は広い.Jisso技術を電気的な側面,特に高速・高周波の観点からとらえると,Interconnect,Packaging,Integration,Multilayer,MEMSなどの技術内容に分類できる.これらの技術内容について現状の課題は山積されているが,ここでは誌面の関係でトピックスのみに絞る.

2.1 Interconnect(内部接続)

電子部品の実装において,比較的大きなエリアを占めるのは半導体ICである.従来はパッケージ化された半導体ICをはんだ付けしていたために,パッケージのリードフレームやBGA(Ball

Grid Array)が大きな面積を占めていた.しかし最近では従来のパッケージは用いずに,半導体ICを直接ベアチップ実装する.それもフェースアップでワイヤボンディングするのではなく,フリップチップ(Flip

Chip)で小型に実装する傾向にある.したがってフリップチップ実装において,信号が通る線路や接続部での損失をいかに少なくするのか,接地をどう確保するのかが重要な課題になる.

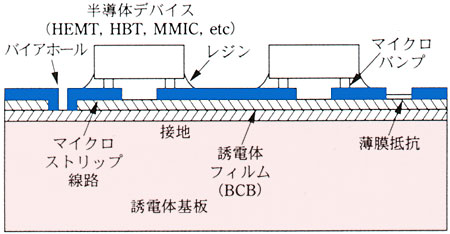

フリップチップ実装の例(7) を図1に示す.図1の例では,BCB(Benzocyclobutene)なる誘電体材料の上にマイクロストリップ線路を形成し,その上にマイクロバンプを介して半導体ICをフリップチップ実装している.ここで電気的な側面,高速・高周波の観点から考えると,

|

①

|

いかに不連続部分をなくし損失を低減するか |

|

②

|

いかに基板側とチップ側の接地間のインダクタンスを低減し,入出力間のアイソレーションを保つか |

|

③

|

基板とチップ間に接着剤を流し込む場合,性能や信頼性の面からどういう材料を選ぶか |

等が課題である.もちろん,①~③を実現させるための等価回路モデリングや電磁界解析手法も重要になる.

図1 フリップチップ実装の例(7)

2.2 Packaging(パッケージング)

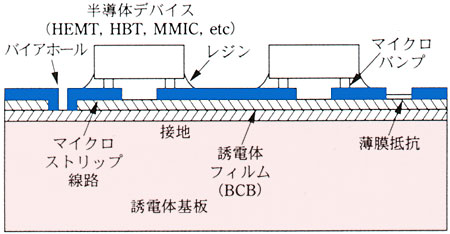

パッケージは以前ではかなりはん用的なものであり,半導体ICと切り離して考えることができた.しかしパッケージと半導体ICで役割分担するSOP(System

on Package)が出現してから様子が一変した.そのパッケージの変遷の様子(8)

を図2に示す.2000年まではパッケージの端子がリードフレームなのかBGAなのかの違いだけで,本質的にパッケージと半導体ICを切り離して議論ができた.図2においてCSPと書かれているのは,現在,電子部品のパッケージの主流になっているChip

Scale Packageのことであり,基本的にMCM(Multi Chip Module)と等価である.

図2 パッケージの変遷の様子(8)

|